## DAC122S085 12-Bit Micro Power DUAL Digital-to-Analog Converter with Rail-to-Rail Output

## **General Description**

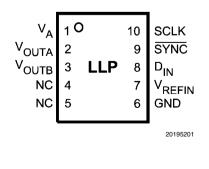

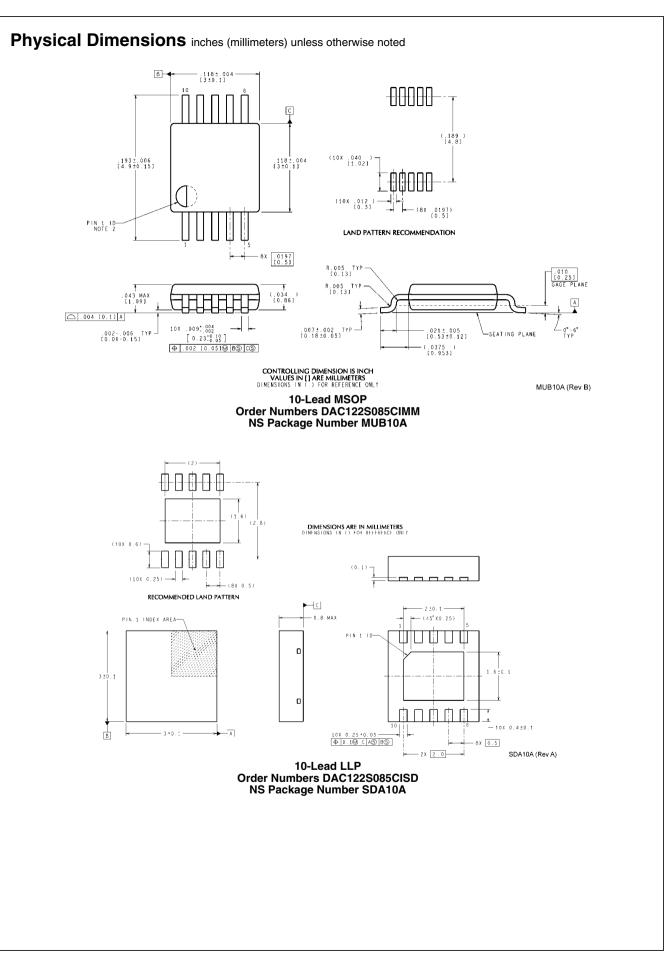

The DAC122S085 is a full-featured, general purpose DUAL 12-bit voltage-output digital-to-analog converter (DAC) that can operate from a single +2.7V to 5.5V supply and consumes 0.6 mW at 3V and 1.6 mW at 5V. The DAC122S085 is packaged in 10-lead LLP and MSOP packages. The 10-lead LLP package makes the DAC122S085 the smallest DUAL DAC in its class. The on-chip output amplifier allows rail-to-rail output swing and the three wire serial interface operates at clock rates up to 40 MHz over the entire supply voltage range. Competitive devices are limited to 25 MHz clock rates at supply voltages in the 2.7V to 3.6V range. The serial interface is compatible with standard SPI<sup>™</sup>, QSPI, MICROWIRE and DSP interfaces.

The reference for the DAC122S085 serves all four channels and can vary in voltage between 1V and  $V_A$ , providing the widest possible output dynamic range. The DAC122S085 has a 16-bit input shift register that controls the outputs to be updated, the mode of operation, the powerdown condition, and the binary input data. Both outputs can be updated simultaneously or individually depending on the setting of the two mode of operation bits.

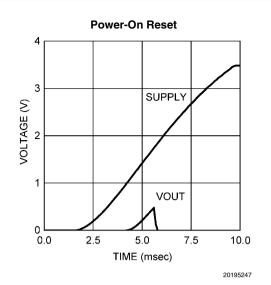

A power-on reset circuit ensures that the DAC output powers up to zero volts and remains there until there is a valid write to the device. A power-down feature reduces power consumption to less than a microWatt with three different termination options.

The low power consumption and small packages of the DAC122S085 make it an excellent choice for use in battery operated equipment.

The DAC122S085 is one of a family of pin compatible DACs, including the 8-bit DAC082S085 and the 10-bit DAC102S085. The DAC122S085 operates over the extended industrial temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

## Pin Configuration

## Features

- Guaranteed Monotonicity

- Low Power Operation

- Rail-to-Rail Voltage Output

- Power-on Reset to 0V

- Simultaneous Output Updating

- Wide power supply range (+2.7V to +5.5V)

- Industry's Smallest Package

- Power Down Modes

## **Key Specifications**

- Resolution 12 bits INL ±8 LSB (max) DNL +0.7 / -0.5 LSB (max) Settling Time 8.5 µs (max) Zero Code Error +15 mV (max) . Full-Scale Error -0.75 %FS (max) Supply Power 0.6 mW (3V) / 1.6 mW (5V) typ -— Normal

- Power Down 0.3 μW (3V) / 0.8 μW (5V) typ

## Applications

- Battery-Powered Instruments

- Digital Gain and Offset Adjustment

- Programmable Voltage & Current Sources

- Programmable Attenuators

DAC122S085 12-Bit Micro Power DUAL Digital-to-Analog Converter with Rail-to-Rail Output

SPI<sup>™</sup> is a trademark of Motorola, Inc.

## Ordering Information

| Order Numbers   | Temperature Range                        | Package                 | Top Mark |

|-----------------|------------------------------------------|-------------------------|----------|

| DAC122S085CISD  | $-40^{\circ}C \le T_A \le +105^{\circ}C$ | LLP                     | X73C     |

| DAC122S085CISDX | $-40^{\circ}C \le T_A \le +105^{\circ}C$ | LLP Tape-and-Reel       | X73C     |

| DAC122S085CIMM  | $-40^{\circ}C \le T_A \le +105^{\circ}C$ | MSOP                    | X72C     |

| DAC122S085CIMMX | $-40^{\circ}C \le T_A \le +105^{\circ}C$ | MSOP Tape-and-Reel      | X72C     |

| DAC122S085EVAL  |                                          | Evaluation Board (MSOP) |          |

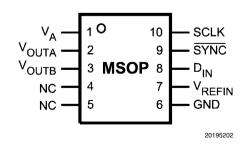

## **Block Diagram**

20195203

| LLP<br>MSOP<br>Pin No. | Symbol             | Туре          | Description                                                                                                                                                                                                                                                                                                                                                            |  |

|------------------------|--------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                      | V <sub>A</sub>     | Supply        | Power supply input. Must be decoupled to GND.                                                                                                                                                                                                                                                                                                                          |  |

| 2                      | V <sub>OUTA</sub>  | Analog Output | Channel A Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                       |  |

| 3                      | V <sub>OUTB</sub>  | Analog Output | Channel B Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                       |  |

| 4                      | NC                 |               | Not Connected                                                                                                                                                                                                                                                                                                                                                          |  |

| 5                      | NC                 |               | Not Connected                                                                                                                                                                                                                                                                                                                                                          |  |

| 6                      | GND                | Ground        | Ground reference for all on-chip circuitry.                                                                                                                                                                                                                                                                                                                            |  |

| 7                      | V <sub>REFIN</sub> | Analog Input  | Unbuffered reference voltage shared by both channels. Must be decoupled to GND.                                                                                                                                                                                                                                                                                        |  |

| 8                      | D <sub>IN</sub>    | Digital Input | Serial Data Input. Data is clocked into the 16-bit shift register on the fa edges of SCLK after the fall of SYNC.                                                                                                                                                                                                                                                      |  |

| 9                      | SYNC               | Digital Input | Frame synchronization input for the data input. When this pin goes low it enables the input shift register and data is transferred on the falling edges of SCLK. The DAC is updated on the 16th clock cycle unless SYNC is brought high before the 16th clock, in which case the rising edg of SYNC acts as an interrupt and the write sequence is ignored by the DAC. |  |

| 10                     | SCLK               | Digital Input | Serial Clock Input. Data is clocked into the input shift register on the falling edges of this pin.                                                                                                                                                                                                                                                                    |  |

| 11                     | PAD<br>(LLP only)  | Ground        | Exposed die attach pad can be connected to ground or left floating.<br>Soldering the pad to the PCB offers optimal thermal performance an<br>enhances package self-alignment during reflow.                                                                                                                                                                            |  |

## Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage, V <sub>A</sub>           | 6.5V            |

|------------------------------------------|-----------------|

| Voltage on any Input Pin                 | -0.3V to 6.5V   |

| Input Current at Any Pin (Note 3)        | 10 mA           |

| Package Input Current (Note 3)           | 20 mA           |

| Power Consumption at $T_A = 25^{\circ}C$ | See (Note 4)    |

| ESD Susceptibility (Note 5)              |                 |

| Human Body Model                         | 2500V           |

| Machine Model                            | 250V            |

| Junction Temperature                     | +150°C          |

| Storage Temperature                      | –65°C to +150°C |

## Operating Ratings (Notes 1, 2)

| Operating Temperature Range           | $-40^{\circ}C \le T_A \le +105^{\circ}C$ |

|---------------------------------------|------------------------------------------|

| Supply Voltage, V <sub>A</sub>        | +2.7V to 5.5V                            |

| Reference Voltage, V <sub>REFIN</sub> | +1.0V to V <sub>A</sub>                  |

| Digital Input Voltage (Note 7)        | 0.0V to 5.5V                             |

| Output Load                           | 0 to 1500 pF                             |

| SCLK Frequency                        | Up to 40 MHz                             |

|                                       |                                          |

## **Package Thermal Resistances**

| Package      | θ <sub>JA</sub> |

|--------------|-----------------|

| 10-Lead MSOP | 240°C/W         |

| 10-Lead LLP  | 250°C/W         |

Soldering process must comply with National Semiconductor's Reflow Temperature Profile specifications. Refer to www.national.com/packaging. (Note 6)

## **Electrical Characteristics**

The following specifications apply for  $V_A = +2.7V$  to +5.5V,  $V_{REFIN} = V_A$ ,  $C_L = 200$  pF to GND,  $f_{SCLK} = 30$  MHz, input code range 48 to 4047. Boldface limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all other limits are at  $T_A = 25^{\circ}$ C, unless otherwise specified.

| Symbol                   | Parameter                                          | Conditions                                     | Typical<br>(Note 9) | Limits<br>(Note 9) | Units<br>(Limits) |

|--------------------------|----------------------------------------------------|------------------------------------------------|---------------------|--------------------|-------------------|

| STATIC PE                | RFORMANCE                                          | •                                              | •                   |                    |                   |

|                          | Resolution                                         |                                                |                     | 12                 | Bits (min)        |

|                          | Monotonicity                                       |                                                |                     | 12                 | Bits (min)        |

| INL                      | Integral Non-Linearity                             |                                                | ±2.4                | ±8                 | LSB (max)         |

|                          |                                                    | $V_{\rm r} = 2.7 V_{\rm r}$ to 5.5 V           | +0.2                | +0.7               | LSB (max)         |

| DNL                      | Differential Non-Linearity                         | V <sub>A</sub> = 2.7V to 5.5V                  | -0.1                | -0.5               | LSB (min)         |

|                          |                                                    | V <sub>A</sub> = 4.5V to 5.5V (Note 10)        | ±0.15               | ±0.5               | LSB (max)         |

| ZE                       | Zero Code Error                                    | $I_{OUT} = 0$                                  | +4                  | +15                | mV (max)          |

| FSE                      | Full-Scale Error                                   | $I_{OUT} = 0$                                  | -0.1                | -0.75              | %FSR (ma>         |

| GE                       | Gain Error                                         | All ones Loaded to DAC register                | -0.2                | -1.0               | %FSR              |

| ZCED                     | Zero Code Error Drift                              |                                                | -20                 |                    | μV/°C             |

| TOOF                     |                                                    | V <sub>A</sub> = 3V                            | -0.7                |                    | ppm/°C            |

| TC GE Gain Error Tempco  |                                                    | V <sub>A</sub> = 5V                            | -1.0                |                    | ppm/°C            |

| OUTPUT C                 | HARACTERISTICS                                     | •                                              |                     |                    |                   |

|                          |                                                    | (Nists 10)                                     |                     | 0                  | V (min)           |

|                          | Output Voltage Range                               | (Note 10)                                      |                     | V <sub>REFIN</sub> | V (max)           |

| I <sub>oz</sub>          | High-Impedance Output Leakage<br>Current (Note 10) |                                                |                     | ±1                 | μA (max)          |

|                          |                                                    | V <sub>A</sub> = 3V, I <sub>OUT</sub> = 200 μA | 1.3                 |                    | mV                |

|                          |                                                    | $V_A = 3V, I_{OUT} = 1 \text{ mA}$             | 6.0                 |                    | mV                |

| ZCO                      | Zero Code Output                                   | V <sub>A</sub> = 5V, I <sub>OUT</sub> = 200 μA | 7.0                 |                    | mV                |

|                          |                                                    | $V_A = 5V, I_{OUT} = 1 \text{ mA}$             | 10.0                |                    | mV                |

|                          |                                                    | V <sub>A</sub> = 3V, I <sub>OUT</sub> = 200 μA | 2.984               |                    | V                 |

|                          |                                                    | $V_A = 3V, I_{OUT} = 1 \text{ mA}$             | 2.934               |                    | V                 |

| FSO                      | Full Scale Output                                  | $V_{A} = 5V, I_{OUT} = 200 \mu A$              | 4.989               |                    | V                 |

|                          |                                                    | $V_{A} = 5V, I_{OUT} = 1 \text{ mA}$           | 4.958               |                    | V                 |

|                          | Output Short Circuit Current                       | $V_A = 3V, V_{OUT} = 0V,$<br>Input Code = FFFh | -56                 |                    | mA                |

| l <sub>os</sub> (source) |                                                    | $V_A = 5V, V_{OUT} = 0V,$<br>Input Code = FFFh | -69                 |                    | mA                |

| Symbol           | Parameter                                                            | Condi                                          | tions                            | Typical<br>(Note 9) | Limits<br>(Note 9) | Units<br>(Limits) |

|------------------|----------------------------------------------------------------------|------------------------------------------------|----------------------------------|---------------------|--------------------|-------------------|

| 1                | Outruit Chart Circuit Current (circle)                               | $V_A = 3V, V_{OUT} = 3V,$<br>Input Code = 000h |                                  | 52                  |                    | mA                |

| I <sub>os</sub>  | Output Short Circuit Current (sink)                                  | $V_A = 5V, V_{OUT} = 5V,$<br>Input Code = 000h |                                  | 75                  |                    | mA                |

| Ι <sub>Ο</sub>   | Continuous Output<br>Current (Note 10)                               | Available on each DA                           | AC output                        |                     | 11                 | mA (max)          |

| 0                |                                                                      | $R_{L} = \infty$                               |                                  | 1500                |                    | pF                |

| CL               | Maximum Load Capacitance                                             | $R_L = 2k\Omega$                               |                                  | 1500                |                    | pF                |

| Z <sub>OUT</sub> | DC Output Impedance                                                  |                                                |                                  | 7.5                 |                    | Ω                 |

|                  | E INPUT CHARACTERISTICS                                              |                                                |                                  |                     |                    |                   |

|                  | Input Range Minimum                                                  |                                                |                                  | 0.2                 | 1.0                | V (min)           |

| VREFIN           | Input Range Maximum                                                  |                                                |                                  |                     | V <sub>A</sub>     | V (max)           |

|                  | Input Impedance                                                      |                                                |                                  | 60                  |                    | kΩ                |

|                  | UT CHARACTERISTICS                                                   |                                                |                                  |                     |                    |                   |

| I <sub>IN</sub>  | Input Current (Note 10)                                              |                                                |                                  |                     | ±1                 | μA (max)          |

| V                |                                                                      | $V_A = 3V$                                     |                                  | 0.9                 | 0.6                | V (max)           |

| V <sub>IL</sub>  | Input Low Voltage (Note 10)                                          | V <sub>A</sub> = 5V                            |                                  | 1.5                 | 0.8                | V (max)           |

|                  |                                                                      | V <sub>A</sub> = 3V                            |                                  | 1.4                 | 2.1                | V (min)           |

| V <sub>IH</sub>  | Input High Voltage (Note 10)                                         | $V_A = 5V$                                     |                                  | 2.1                 | 2.4                | V (min)           |

| C <sub>IN</sub>  | Input Capacitance (Note 10)                                          |                                                |                                  |                     | 3                  | pF (max)          |

|                  | QUIREMENTS                                                           |                                                |                                  |                     | _                  | P ( ~ 7           |

|                  | Supply Voltage Minimum                                               |                                                |                                  |                     | 2.7                | V (min)           |

| V <sub>A</sub>   | Supply Voltage Maximum                                               |                                                |                                  |                     | 5.5                | V (max)           |

|                  |                                                                      |                                                | V <sub>A</sub> = 2.7V<br>to 3.6V | 210                 | 270                | μA (max)          |

|                  | Normal Supply Current (output                                        | f <sub>SCLK</sub> = 30 MHz                     | V <sub>A</sub> = 4.5V<br>to 5.5V | 320                 | 410                | μA (max)          |

| I <sub>N</sub>   | unloaded)                                                            | £ 0                                            | V <sub>A</sub> = 2.7V<br>to 3.6V | 190                 |                    | μΑ                |

|                  |                                                                      | f <sub>SCLK</sub> = 0                          | V <sub>A</sub> = 4.5V<br>to 5.5V | 290                 |                    | μA                |

| I                | Power Down Supply Current (output<br>unloaded, SYNC = DIN = 0V after | All PD Modes,                                  | V <sub>A</sub> = 2.7V<br>to 3.6V | 0.1                 | 1.0                | μA (max)          |

| I <sub>PD</sub>  | PD mode loaded)                                                      | (Note 10)                                      | V <sub>A</sub> = 4.5V<br>to 5.5V | 0.15                | 1.0                | µA (max)          |

|                  |                                                                      | f <sub>SCLK</sub> = 30 MHz                     | V <sub>A</sub> = 2.7V<br>to 3.6V | 0.6                 | 1.0                | mW (max)          |

| P <sub>N</sub>   | Normal Supply Power (output                                          |                                                | V <sub>A</sub> = 4.5V<br>to 5.5V | 1.6                 | 2.3                | mW (max)          |

| ' N              | unloaded)                                                            | f <sub>SCLK</sub> = 0                          | V <sub>A</sub> = 2.7V<br>to 3.6V | 0.6                 |                    | mW                |

|                  |                                                                      | SULK - V                                       | V <sub>A</sub> = 4.5V<br>to 5.5V | 1.5                 |                    | mW                |

| P <sub>PD</sub>  | Power Down Supply Power (output<br>unloaded, SYNC = DIN = 0V after   | All PD Modes,                                  | V <sub>A</sub> = 2.7V<br>to 3.6V | 0.3                 | 3.6                | µW (max)          |

| ' PD             | PD mode loaded)                                                      | (Note 10) $V_A = 4.5V$<br>to 5.5V              |                                  | 0.8                 | 5.5                | µW (max)          |

## A.C. and Timing Characteristics

Values shown in this table are design targets and are subject to change before product release.

The following specifications apply for  $V_A = +2.7V$  to +5.5V,  $V_{REFIN} = V_A$ ,  $C_L = 200$  pF to GND,  $f_{SCLK} = 30$  MHz, input code range 48 to 4047. Boldface limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all other limits are at  $T_A = 25^{\circ}$ C, unless otherwise specified.

| Symbol              | Parameter                                                                                        | Conductions                                                 | Typical<br>(Note 9) | Limits<br>(Note 9) | Units<br>(Limits) |

|---------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------|--------------------|-------------------|

| f <sub>SCLK</sub>   | SCLK Frequency                                                                                   |                                                             | 40                  | 30                 | MHz (max)         |

| t <sub>s</sub>      | Output Voltage Settling Time400h to C00h code change(Note 10) $R_L = 2 k\Omega$ , $C_L = 200 pF$ |                                                             | 6                   | 8.5                | µs (max)          |

| SR                  | Output Slew Rate                                                                                 |                                                             | 1                   |                    | V/µs              |

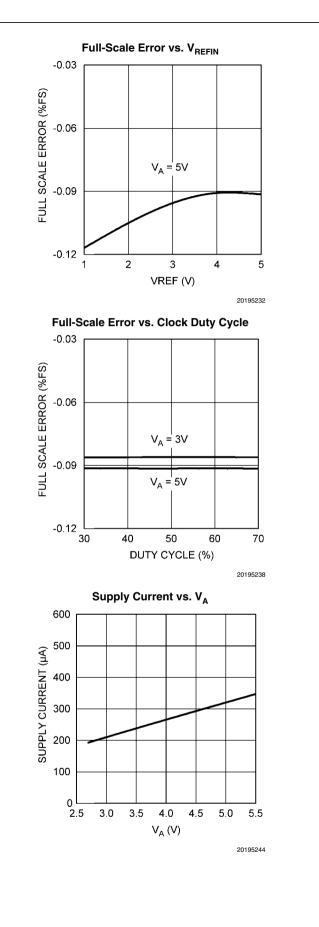

|                     | Glitch Impulse                                                                                   | Code change from 800h to 7FFh                               | 12                  |                    | nV-sec            |

|                     | Digital Feedthrough                                                                              |                                                             | 0.5                 |                    | nV-sec            |

|                     | Digital Crosstalk                                                                                |                                                             | 1                   |                    | nV-sec            |

|                     | DAC-to-DAC Crosstalk                                                                             |                                                             | 3                   |                    | nV-sec            |

|                     | Multiplying Bandwidth                                                                            | $V_{\text{REFIN}} = 2.5V \pm 0.1Vpp$                        | 160                 |                    | kHz               |

|                     | Total Harmonic Distortion                                                                        | V <sub>REFIN</sub> = 2.5V ± 1Vpp<br>input frequency = 10kHz | 70                  |                    | dB                |

|                     | $V_A = 3V$                                                                                       | 6                                                           |                     | µsec               |                   |

| wu                  | Wake-Up Time                                                                                     | $V_A = 5V$                                                  | 39                  |                    | µsec              |

| 1/f <sub>SCLK</sub> | SCLK Cycle Time                                                                                  |                                                             | 25                  | 33                 | ns (min)          |

| сн                  | SCLK High time                                                                                   |                                                             | 7                   | 10                 | ns (min)          |

| CL                  | SCLK Low Time                                                                                    |                                                             | 7                   | 10                 | ns (min)          |

| SS                  | SYNC Set-up Time prior to SCLK<br>Falling Edge                                                   |                                                             | 4                   | 10                 | ns (min)          |

| DS                  | Data Set-Up Time prior to SCLK<br>Falling Edge                                                   |                                                             | 1.5                 | 3.5                | ns (min)          |

| DH                  | Data Hold Time after SCLK Falling<br>Edge                                                        |                                                             | 1.5                 | 3.5                | ns (min)          |

| CFSR                | SCLK fall prior to rise of SYNC                                                                  |                                                             | 0                   | 3                  | ns (min)          |

| SYNC                | SYNC High Time                                                                                   |                                                             | 6                   | 10                 | ns (min)          |

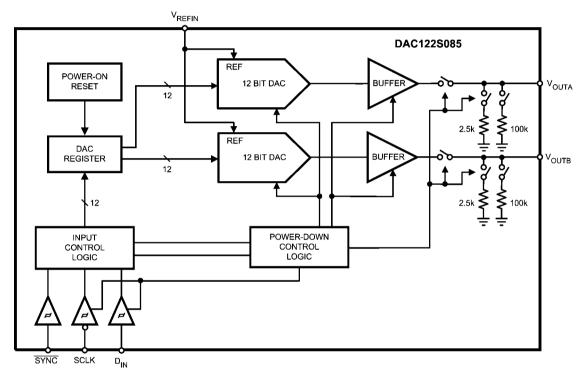

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

Note 2: All voltages are measured with respect to GND = 0V, unless otherwise specified.

Note 3: When the input voltage at any pin exceeds 5.5V or is less than GND, the current at that pin should be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two.

**Note 4:** The absolute maximum junction temperature ( $T_Jmax$ ) for this device is 150°C. The maximum allowable power dissipation is dictated by  $T_Jmax$ , the junction-to-ambient thermal resistance ( $\theta_{JA}$ ), and the ambient temperature ( $T_A$ ), and can be calculated using the formula  $P_DMAX = (T_Jmax - T_A) / \theta_{JA}$ . The values for maximum power dissipation will be reached only when the device is operated in a severe fault condition (e.g., when input or output pins are driven beyond the operating ratings, or the power supply polarity is reversed).

Note 5: Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through ZERO Ohms.

**Note 6:** Reflow temperature profiles are different for lead-free packages.

**Note 7:** The inputs are protected as shown below. Input voltage magnitudes up to 5.5V, regardless of  $V_A$ , will not cause errors in the conversion result. For example, if  $V_A$  is 3V, the digital input pins can be driven with a 5V logic device.

Note 8: To guarantee accuracy, it is required that  $V_A$  and  $V_{REFIN}$  be well bypassed.

Note 9: Typical figures are at T<sub>J</sub> = 25°C, and represent most likely parametric norms. Test limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 10: This parameter is guaranteed by design and/or characterization and is not tested in production.

## **Specification Definitions**

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB, which is  $V_{\text{RFF}} / 4096 = V_{\text{A}} / 4096$ .

**DAC-to-DAC CROSSTALK** is the glitch impulse transferred to a DAC output in response to a full-scale change in the output of another DAC.

**DIGITAL CROSSTALK** is the glitch impulse transferred to a DAC output at mid-scale in response to a full-scale change in the input register of another DAC.

**DIGITAL FEEDTHROUGH** is a measure of the energy injected into the analog output of the DAC from the digital inputs when the DAC outputs are not updated. It is measured with a full-scale code change on the data bus.

**FULL-SCALE ERROR** is the difference between the actual output voltage with a full scale code (FFFh) loaded into the DAC and the value of  $V_A \times 4095 / 4096$ .

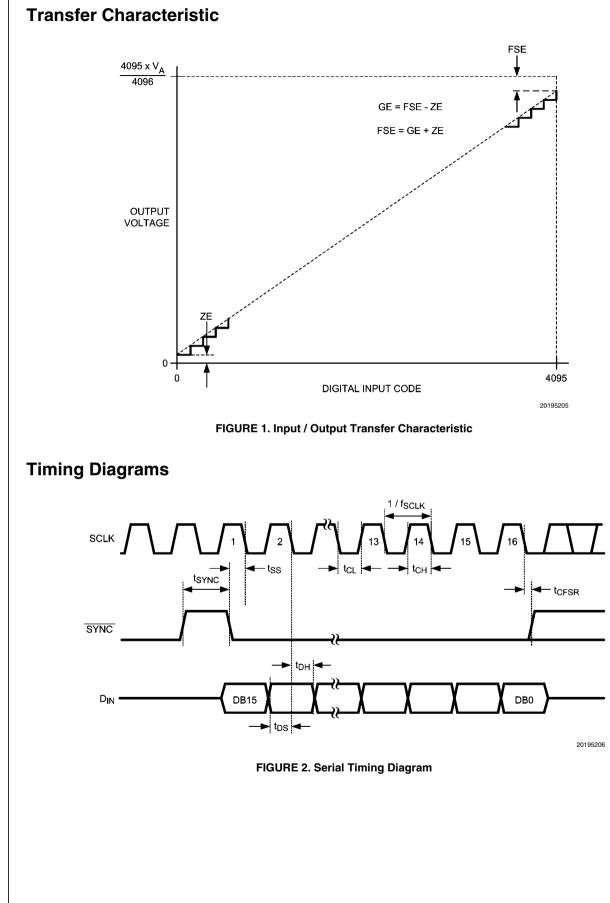

**GAIN ERROR** is the deviation from the ideal slope of the transfer function. It can be calculated from Zero and Full-Scale Errors as GE = FSE - ZE, where GE is Gain error, FSE is Full-Scale Error and ZE is Zero Error.

**GLITCH IMPULSE** is the energy injected into the analog output when the input code to the DAC register changes. It is specified as the area of the glitch in nanovolt-seconds.

**INTEGRAL NON-LINEARITY (INL)** is a measure of the deviation of each individual code from a straight line through the input to output transfer function. The deviation of any given code from this straight line is measured from the center of that code value. The end point method is used. INL for this product is specified over a limited range, per the Electrical Tables.

LEAST SIGNIFICANT BIT (LSB) is the bit that has the smallest value or weight of all bits in a word. This value is

#### $LSB = V_{BEE} / 2^n$

where  $V_{REF}$  is the supply voltage for this product, and "n" is the DAC resolution in bits, which is 12 for the DAC122S085.

**MAXIMUM LOAD CAPACITANCE** is the maximum capacitance that can be driven by the DAC with output stability maintained.

**MONOTONICITY** is the condition of being monotonic, where the DAC has an output that never decreases when the input code increases.

**MOST SIGNIFICANT BIT (MSB)** is the bit that has the largest value or weight of all bits in a word. Its value is 1/2 of  $V_A$ .

**POWER EFFICIENCY** is the ratio of the output current to the total supply current. The output current comes from the power supply. The difference between the supply and output currents is the power consumed by the device without a load.

**SETTLING TIME** is the time for the output to settle to within 1/2 LSB of the final value after the input code is updated.

**TOTAL HARMONIC DISTORTION (THD)** is the measure of the harmonics present at the output of the DACs with an ideal sine wave applied to  $V_{\text{REFIN}}$ . THD is measured in dB.

**WAKE-UP TIME** is the time for the output to exit power-down mode. This is the time from the falling edge of the 16th SCLK pulse to when the output voltage deviates from the power-down voltage of 0V.

**ZERO CODE ERROR** is the output error, or voltage, present at the DAC output after a code of 000h has been entered.

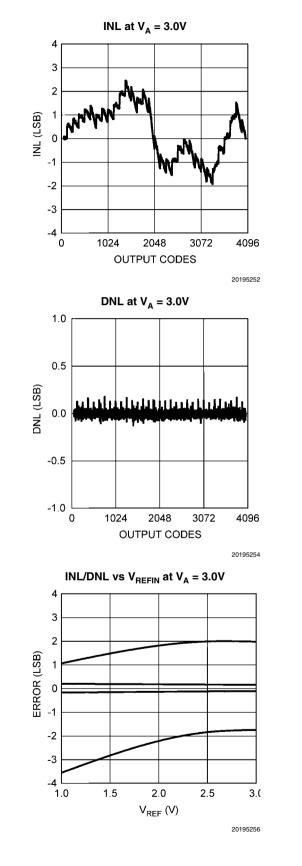

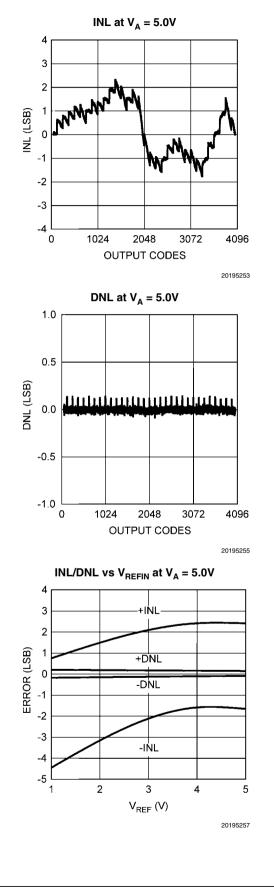

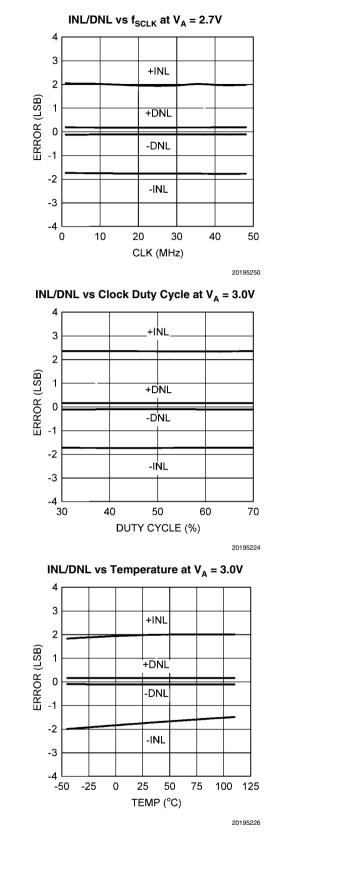

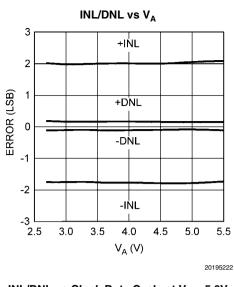

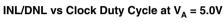

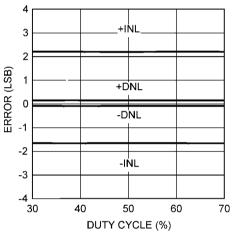

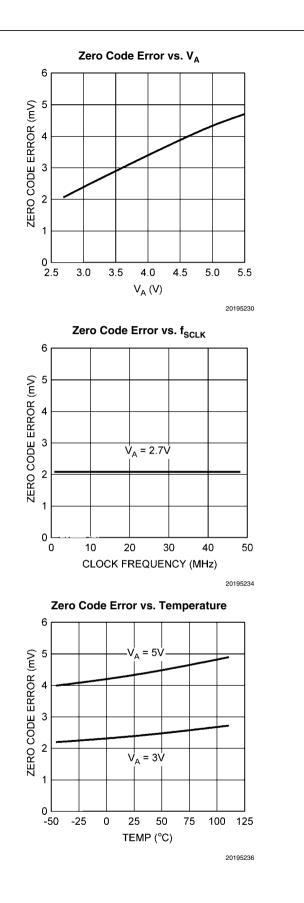

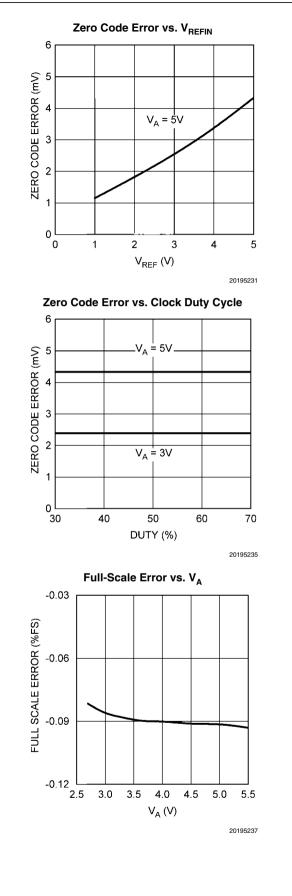

## **Typical Performance Characteristics** $V_{REF} = V_A$ , $f_{SCLK} = 30$ MHz, $T_A = 25C$ , Input Code Range 48 to 4047, unless otherwise stated

20195225

INL/DNL vs Temperature at  $V_A = 5.0V$

20195227

www.national.com

## **1.0 Functional Description**

#### **1.1 DAC SECTION**

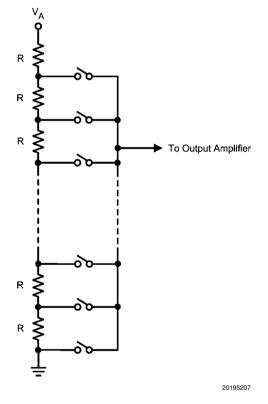

The DAC122S085 is fabricated on a CMOS process with an architecture that consists of switches and resistor strings that are followed by an output buffer. The reference voltage is externally applied at  $V_{\mathsf{REFIN}}$  and is shared by all four DACs.

For simplicity, a single resistor string is shown in *Figure 3*. This string consists of 4096 equal valued resistors with a switch at each junction of two resistors, plus a switch to ground. The code loaded into the DAC register determines which switch is closed, connecting the proper node to the amplifier. The input coding is straight binary with an ideal output voltage of:

#### $V_{OUTA,B} = V_{REFIN} \times (D / 4096)$

where D is the decimal equivalent of the binary code that is loaded into the DAC register. D can take on any value between 0 and 4095. This configuration guarantees that the DAC is monotonic.

FIGURE 3. DAC Resistor String

#### **1.2 OUTPUT AMPLIFIERS**

The output amplifiers are rail-to-rail, providing an output voltage range of 0V to  $V_A$  when the reference is  $V_A$ . All amplifiers, even rail-to-rail types, exhibit a loss of linearity as the output approaches the supply rails (0V and  $V_A$ , in this case). For this

reason, linearity is specified over less than the full output range of the DAC. However, if the reference is less than  $V_A$ , there is only a loss in linearity in the lowest codes. The output capabilities of the amplifier are described in the Electrical Tables.

The output amplifiers are capable of driving a load of  $2 k\Omega$  in parallel with 1500 pF to ground or to  $V_A$ . The zero-code and full-scale outputs for given load currents are available in the Electrical Characterisics Table.

#### **1.3 RERENCE VOLTAGE**

The DAC122S085 uses a single external reference that is shared by both channels. The reference pin,  $V_{\text{REFIN}}$ , is not buffered and has an input impedance of 60 k $\Omega$ . It is recommended that  $V_{\text{REFIN}}$  be driven by a voltage source with low output impedance. The reference voltage range is 1.0V to  $V_{\text{A}}$ , providing the widest possible output dynamic range.

#### **1.4 SERIAL INTERFACE**

The three-wire interface is compatible with SPI, QSPI and MICROWIRE, as well as most DSPs and operates at clock rates up to 40 MHz. See the Timing Diagram for information on a write sequence.

A write sequence begins by bringing the  $\overline{SYNC}$  line low. Once  $\overline{SYNC}$  is low, the data on the D<sub>IN</sub> line is clocked into the 16bit serial input register on the falling edges of SCLK. To avoid misclocking data into the shift register, it is critical that  $\overline{SYNC}$  not be brought low simultaneously with a falling edge of SCLK (see Serial Timing Diagram, *Figure 2*). On the 16th falling clock edge, the last data bit is clocked in and the programmed function (a change in the DAC channel address, mode of operation and/or register contents) is executed. At this point the  $\overline{SYNC}$  line may be kept low or brought high. Any data and clock pusles after the 16th falling clock edge will be ignored. In either case,  $\overline{SYNC}$  must be brought high for the minimum specified time before the next write sequence is initiated with a falling edge of  $\overline{SYNC}$ .

Since the  $\overline{\text{SYNC}}$  and  $D_{\text{IN}}$  buffers draw more current when they are high, they should be idled low between write sequences to minimize power consumption.

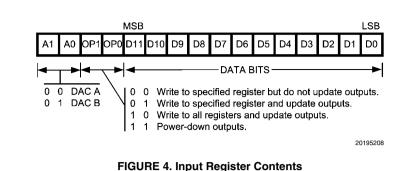

#### **1.5 INPUT SHIFT REGISTER**

The input shift register, *Figure 4*, has sixteen bits. The first bit must be set to "0" and the second bit is an address bit. The address bit determines whether the register data is for DAC A or DAC B. This bit is followed by two bits that determine the mode of operation (writing to a DAC register without updating the outputs of both DACs, writing to a DAC register and updating the outputs of both DACs, writing to the register of both DACs and updating their outputs, or powering down both outputs). The final twelve bits of the shift register are the data bits. The data format is straight binary (MSB first, LSB last), with all 0's corresponding to an output of 0V and all 1's corresponding to a full-scale output of V<sub>REFIN</sub> - 1 LSB. The contents of the serial input register are transferred to the DAC register on the sixteenth falling edge of SCLK. See Timing Diagram, *Figure 2*.

Normally, the SYNC line is kept low for at least 16 falling edges of SCLK and the DAC is updated on the 16th SCLK falling edge. However, if SYNC is brought high before the 16th falling edge, the data transfer to the shift register is aborted and the write sequence is invalid. Under this condition, the DAC register is not updated and there is no change in the mode of operation or in the DAC output voltages.

#### **1.6 POWER-ON RESET**

The power-on reset circuit controls the output voltages both DACs during power-up. Upon application of power, the DAC registers are filled with zeros and the output voltages are 0V. The outputs remain at 0V until a valid write sequence is made to the DAC.

#### **1.7 POWER-DOWN MODES**

The DAC122S085 has four power-down modes, two of which are identical. In power-down mode, the supply current drops to 20  $\mu$ A at 3V and 30  $\mu$ A at 5V. The DAC122S085 is set in power-down mode by setting OP1 and OP0 to 11. Since this mode powers down both DACs, the first two bits of the shift register are used to select different output terminations for the DAC outputs. Setting A1 and A0 to 00 or 11 causes the outputs to be tri-stated (a high impedance state). While setting A1 and A0 to 01 or 10 causes the outputs to be terminated by 2.5 k $\Omega$  or 100 k $\Omega$  to ground respectively (see *Table 1*).

| A1 | A0 | OP1 | OP0 | Operating Mode        |

|----|----|-----|-----|-----------------------|

| 0  | 0  | 1   | 1   | High-Z outputs        |

| 0  | 1  | 1   | 1   | 2.5 k $\Omega$ to GND |

| 1  | 0  | 1   | 1   | 100 kΩ to GND         |

| 1  | 1  | 1   | 1   | High-Z outputs        |

| TABLE | 1 | Power-Down  | Modes |

|-------|---|-------------|-------|

| IADLL |   | FOWEI-DOWII | Modes |

The bias generator, output amplifiers, resistor strings, and other linear circuitry are all shut down in any of the powerdown modes. However, the contents of the DAC registers are unaffected when in power-down. Each DAC register maintains its value prior to the DAC122S085 being powered down unless it is changed during the write sequence which instructed it to recover from power down. Minimum power consumption is achieved in the power-down mode with  $\overline{SYNC}$  and  $D_{\rm IN}$  idled low and SCLK disabled. The time to exit power-down (Wake-Up Time) is typically  $t_{\rm WU}$  µsec as stated in the A.C. and Timing Characteristics table.

## **2.0 Applications Information**

#### 2.1 USING REFERENCES AS POWER SUPPLIES

While the simplicity of the DAC122S085 implies ease of use, it is important to recognize that the path from the reference input ( $V_{REFIN}$ ) to the VOUTs will have essentially zero Power Supply Rejection Ratio (PSRR). Therefore, it is necessary to provide a noise-free supply voltage to  $V_{REFIN}$ . In order to utilize the full dynamic range of the DAC122S085, the supply pin ( $V_A$ ) and  $V_{REFIN}$  can be connected together and share the same supply voltage. Since the DAC122S085 consumes very little power, a reference source may be used as the reference input and/or the supply voltage. The advantages of using a reference source over a voltage regulator are accuracy and stability. Some low noise regulators can also be used. Listed below are a few reference and power supply options for the DAC122S085.

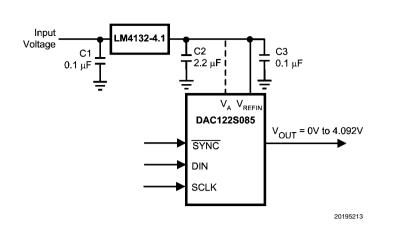

#### 2.1.1 LM4130

The LM4130, with its 0.05% accuracy over temperature, is a good choice as a reference source for the DAC122S085. The 4.096V version is useful if a 0 to 4.095V output range is desirable or acceptable. Bypassing the LM4130 VIN pin with a 0.1 $\mu$ F capacitor and the VOUT pin with a 2.2 $\mu$ F capacitor will improve stability and reduce output noise. The LM4130 comes in a space-saving 5-pin SOT23.

FIGURE 5. The LM4130 as a power supply

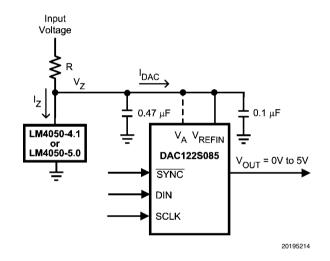

#### 2.1.2 LM4050

Available with accuracy of 0.44%, the LM4050 shunt reference is also a good choice as a reference for the DAC122S085. It is available in 4.096V and 5V versions and comes in a space-saving 3-pin SOT23.

FIGURE 6. The LM4050 as a power supply

The minimum resistor value in the circuit of *Figure 6* must be chosen such that the maximum current through the LM4050 does not exceed its 15 mA rating. The conditions for maximum current include the input voltage at its maximum, the

LM4050 voltage at its minimum, and the DAC122S085 drawing zero current. The maximum resistor value must allow the LM4050 to draw more than its minimum current for regulation plus the maximum DAC122S085 current in full operation. The conditions for minimum current include the input voltage at its minimum, the LM4050 voltage at its maximum, the resistor value at its maximum due to tolerance, and the DAC122S085 draws its maximum current. These conditions can be summarized as

$$R(min) = (V_{IN}(max) - V_{Z}(min)) / I_{Z}(max)$$

and

$$R(max) = (V_{IN}(min) - V_{Z}(max)) / ((I_{DAC}(max) + I_{Z}(min)))$$

where  $V_Z(min)$  and  $V_Z(max)$  are the nominal LM4050 output voltages ± the LM4050 output tolerance over temperature,  $I_Z$  (max) is the maximum allowable current through the LM4050,  $I_Z(min)$  is the minimum current required by the LM4050 for proper regulation, and  $I_{DAC}(max)$  is the maximum DAC122S085 supply current.

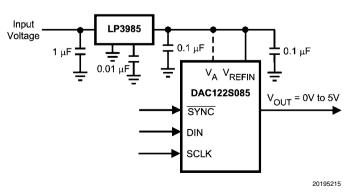

#### 2.1.3 LP3985

The LP3985 is a low noise, ultra low dropout voltage regulator with a 3% accuracy over temperature. It is a good choice for applications that do not require a precision reference for the DAC122S085. It comes in 3.0V, 3.3V and 5V versions, among others, and sports a low 30  $\mu$ V noise specification at low frequencies. Since low frequency noise is relatively difficult to filter, this specification could be important for some applications. The LP3985 comes in a space-saving 5-pin SOT23 and 5-bump micro SMD packages.

FIGURE 7. Using the LP3985 regulator

An input capacitance of  $1.0\mu$ F without any ESR requirement is required at the LP3985 input, while a  $1.0\mu$ F ceramic capacitor with an ESR requirement of  $5m\Omega$  to  $500m\Omega$  is required at the output. Careful interpretation and understanding of the capacitor specification is required to ensure correct device operation.

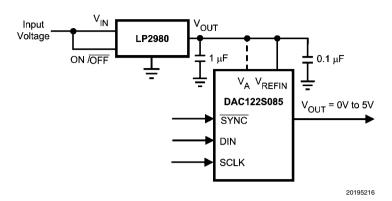

#### 2.1.4 LP2980

The LP2980 is an ultra low dropout regulator with a 0.5% or 1.0% accuracy over temperature, depending upon grade. It is available in 3.0V, 3.3V and 5V versions, among others.

FIGURE 8. Using the LP2980 regulator

Like any low dropout regulator, the LP2980 requires an output capacitor for loop stability. This output capacitor must be at least  $1.0\mu$ F over temperature, but values of  $2.2\mu$ F or more will provide even better performance. The ESR of this capacitor should be within the range specified in the LP2980 data sheet. Surface-mount solid tantalum capacitors offer a good combination of small size and ESR. Ceramic capacitors are attractive due to their small size but generally have ESR values that are too low for use with the LP2980. Aluminum electrolytic capacitors are typically not a good choice due to their large

size and have ESR values that may be too high at low temperatures.

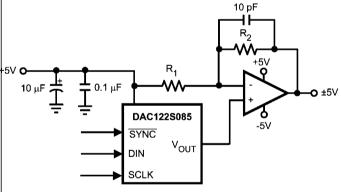

#### 2.2 BIPOLAR OPERATION

The DAC122S085 is designed for single supply operation and thus has a unipolar output. However, a bipolar output may be obtained with the circuit in *Figure 9*. This circuit will provide an output voltage range of  $\pm 5$  Volts. A rail-to-rail amplifier should be used if the amplifier supplies are limited to  $\pm 5V$ .

FIGURE 9. Bipolar Operation

The output voltage of this circuit for any code is found to be

$V_{O} = (V_{A} \times (D / 4096) \times ((R1 + R2) / R1) - V_{A} \times R2 / R1)$

where D is the input code in decimal form. With  $V_{\text{A}}$  = 5V and R1 = R2,

A list of rail-to-rail amplifiers suitable for this application are indicated in *Table 2*.

| TABLE 2. Some Hail-to-Hail Amplifiers |         |                     |                         |  |  |  |

|---------------------------------------|---------|---------------------|-------------------------|--|--|--|

| AMP                                   | PKGS    | Typ V <sub>os</sub> | Typ I <sub>SUPPLY</sub> |  |  |  |

| LMC7111                               | DIP-8   | 0.9 mV              | 25 µA                   |  |  |  |

| LINC/TTT                              | SOT23-5 | 0.9 111             | 25 μΑ                   |  |  |  |

| LM7301                                | SO-8    | 0.03 mV             | 620 µA                  |  |  |  |

| EM7 501                               | SOT23-5 | 0.03 111            | 020 μΑ                  |  |  |  |

| LM8261                                | SOT23-5 | 0.7 mV              | 1 mA                    |  |  |  |

#### **TABLE 2. Some Rail-to-Rail Amplifiers**

#### 2.3 DSP/MICROPROCESSOR INTERFACING

Interfacing the DAC122S085 to microprocessors and DSPs is quite simple. The following guidelines are offered to hasten the design process.

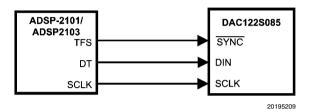

#### 2.3.1 ADSP-2101/ADSP2103 Interfacing

*Figure 10* shows a serial interface between the DAC122S085 and the ADSP-2101/ADSP2103. The DSP should be set to operate in the SPORT Transmit Alternate Framing Mode. It is programmed through the SPORT control register and should be configured for Internal Clock Operation, Active Low Framing and 16-bit Word Length. Transmission is started by writing a word to the Tx register after the SPORT mode has been enabled.

FIGURE 10. ADSP-2101/2103 Interface

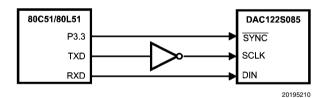

#### 2.3.2 80C51/80L51 Interface

A serial interface between the DAC122S085 and the 80C51/80L51 microcontroller is shown in *Figure 11*. The SYNC signal comes from a bit-programmable pin on the microcontroller. The example shown here uses port line P3.3. This line is taken low when data is transmitted to the DAC122S085. Since the 80C51/80L51 transmits 8-bit bytes, only eight falling clock edges occur in the transmit cycle. To load data into the DAC, the P3.3 line must be left low after the first eight bits are transmitted. A second write cycle is initiated to transmit the second byte of data, after which port line P3.3 is brought high. The 80C51/80L51 transmit routine must recognize that the 80C51/80L51 transmits data with the LSB first while the DAC122S085 requires data with the MSB first.

FIGURE 11. 80C51/80L51 Interface

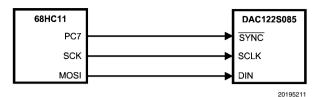

#### 2.3.3 68HC11 Interface

A serial interface between the DAC122S085 and the 68HC11 microcontroller is shown in *Figure 12*. The SYNC line of the DAC122S085 is driven from a port line (PC7 in the figure), similar to the 80C51/80L51.

The 68HC11 should be configured with its CPOL bit as a zero and its CPHA bit as a one. This configuration causes data on the MOSI output to be valid on the falling edge of SCLK. PC7 is taken low to transmit data to the DAC. The 68HC11 transmits data in 8-bit bytes with eight falling clock edges. Data is transmitted with the MSB first. PC7 must remain low after the first eight bits are transferred. A second write cycle is initiated to transmit the second byte of data to the DAC, after which PC7 should be raised to end the write sequence.

FIGURE 12. 68HC11 Interface

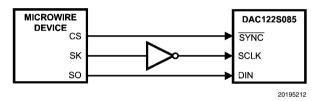

#### 2.3.4 Microwire Interface

*Figure 13* shows an interface between a Microwire compatible device and the DAC122S085. Data is clocked out on the rising edges of the SK signal. As a result, the SK of the Microwire device needs to be inverted before driving the SCLK of the DAC122S085.

FIGURE 13. Microwire Interface

#### 2.4 LAYOUT, GROUNDING, AND BYPASSING

For best accuracy and minimum noise, the printed circuit board containing the DAC122S085 should have separate analog and digital areas. The areas are defined by the locations of the analog and digital power planes. Both of these planes should be located in the same board layer. There should be a single ground plane. A single ground plane is preferred if digital return current does not flow through the analog ground area. Frequently a single ground plane design will utilize a "fencing" technique to prevent the mixing of analog and digital ground current. Separate ground planes should only be utilized when the fencing technique is inadequate. The separate ground planes must be connected in one place, preferably near the DAC122S085. Special care is required to guarantee that digital signals with fast edge rates do not pass over split ground planes. They must always have a continuous return path below their traces.

The DAC122S085 power supply should be bypassed with a 10µF and a 0.1µF capacitor as close as possible to the device with the 0.1µF right at the device supply pin. The 10µF capacitor should be a tantalum type and the 0.1µF capacitor should be a low ESL, low ESR type. The power supply for the DAC122S085 should only be used for analog circuits.

Avoid crossover of analog and digital signals and keep the clock and data lines on the component side of the board. The clock and data lines should have controlled impedances.

## Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | De                      | sign Support                   |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools          | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes               | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs       | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                 | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards             | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging               | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance        | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors            | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support        | www.national.com/feedback      |

| Voltage Reference              | www.national.com/vref        | Design Made Easy        | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions               | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | Solar Magic®            | www.national.com/solarmagic    |

| Wireless (PLL/VCO)             | www.national.com/wireless    | Analog University®      | www.national.com/AU            |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com